UVC LED相關(guān)技術(shù)原理

- 時(shí)間:2022-01-27作者:深圳市科電電子有限公司瀏覽:597

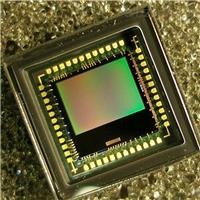

深圳市科電電子有限公司專注于FPGA廠家,sensor廠家,LDO廠家,UVC,儲(chǔ)存快充芯片,環(huán)境光距離傳感器等

詞條

詞條說明

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個(gè)概念,內(nèi)部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸入輸出模塊IOB(Input Output Block)和內(nèi)部連線(Interconnect)三個(gè)部分。 現(xiàn)場(chǎng)可編程門陣列(FPGA)是可編程器件,與傳統(tǒng)邏輯電路和門陣列(如PAL,GAL及CPLD器件)相比,F(xiàn)PGA具有不同的結(jié)構(gòu)。

1. 何為UVC??首先,我們復(fù)習(xí)一下UV的概念。UV,即Ultraviolet,也就是紫外線,為波長在10nm至400nm之間的電磁波。不同波段的UV又可劃分為UVA、UVB、UVC。UVA:波長較長,波長介于320-400nm,可穿透云層、玻璃進(jìn)入室內(nèi)及車內(nèi),可穿透至皮膚真皮層,會(huì)造成曬黑。UVA可再細(xì)分為UVA-2(320-340nm)與UVA-1(340-400nm)。UVB:波

FPGA的優(yōu)點(diǎn)如下:?(1) FPGA由邏輯單元、RAM、乘法器等硬件資源組成,通過將這些硬件資源合理組織,可實(shí)現(xiàn)乘法器、寄存器、地址發(fā)生器等硬件電路。(2) FPGA可通過使用框圖或者Verilog HDL來設(shè)計(jì),從簡單的門電路到FIR或者FFT電路。(3) FPGA可無限地重新編程,加載一個(gè)新的設(shè)計(jì)方案只需幾百毫秒,利用重配置可以減少硬件的開銷。(4) FPGA的工作頻率由FPGA芯

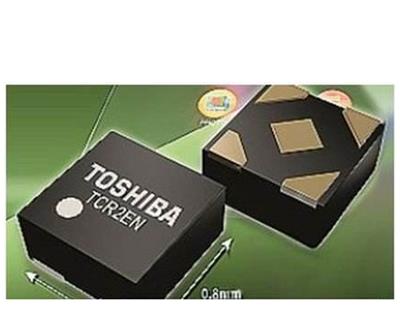

LDO的應(yīng)用非常簡單,很多LDO僅需在輸入端及輸出端各接一顆電容即可穩(wěn)定工作。在LDO的應(yīng)用中需要考慮壓差、靜態(tài)電流、PSRR等重要參數(shù)。在以電池作為電源的系統(tǒng)中,應(yīng)當(dāng)選擇壓差盡量低的LDO,這樣可以使電池較長時(shí)間為系統(tǒng)供電,比如NCP600,NCP629等等。靜態(tài)電流Iq是Iquiescent的縮寫,指芯片自身所消耗的電流。在一些低功耗應(yīng)用中,應(yīng)當(dāng)盡量選擇Iq小的LDO。一些工程師在設(shè)計(jì)低功耗系

聯(lián)系方式 聯(lián)系我時(shí),請(qǐng)告知來自八方資源網(wǎng)!

公司名: 深圳市科電電子有限公司

聯(lián)系人: 聶紹明

電 話: 13243662666

手 機(jī): 13823729687

微 信: 13823729687

地 址: 廣東深圳寶安區(qū)31區(qū)水口花園6片37號(hào)205

郵 編:

網(wǎng) 址: chuangke18.b2b168.com

相關(guān)推薦

相關(guān)閱讀

1、本信息由八方資源網(wǎng)用戶發(fā)布,八方資源網(wǎng)不介入任何交易過程,請(qǐng)自行甄別其真實(shí)性及合法性;

2、跟進(jìn)信息之前,請(qǐng)仔細(xì)核驗(yàn)對(duì)方資質(zhì),所有預(yù)付定金或付款至個(gè)人賬戶的行為,均存在詐騙風(fēng)險(xiǎn),請(qǐng)?zhí)岣呔瑁?

- 聯(lián)系方式

公司名: 深圳市科電電子有限公司

聯(lián)系人: 聶紹明

手 機(jī): 13823729687

電 話: 13243662666

地 址: 廣東深圳寶安區(qū)31區(qū)水口花園6片37號(hào)205

郵 編:

網(wǎng) 址: chuangke18.b2b168.com

- 相關(guān)企業(yè)

- 深圳市宇正芯科技有限公司

- 深圳市恒辰微電子有限公司

- 深圳市光達(dá)電子有限公司

- 四川芯毅光通信科技有限公司

- 深圳市岳邦電子科技有限公司

- 深圳市沃德一佳科技有限公司

- 深圳市悅為光電科技有限公司

- 深圳市鑫永誠光電科技有限公司

- 泉州市速冠電子科技有限公司

- 寧波市浩天電子有限公司

- 商家產(chǎn)品系列

- ito導(dǎo)電膜

- led

- led白色芯片

- led背光板

- led背光源

- led壁燈

- led變色燈

- led彩燈

- led彩虹管

- led彩幕

- led草坪燈

- led側(cè)背光

- led導(dǎo)光板

- led燈帶

- led燈具加工廠

- led燈具設(shè)計(jì)

- led燈泡

- led燈飾配件

- led點(diǎn)陣

- led電路板

- led吊燈

- led發(fā)光管

- led發(fā)光條

- led反射膜

- led防爆燈

- led防靜電服

- led防水電源線

- led封裝設(shè)備

- led工礦燈

- led工藝燈

- 產(chǎn)品推薦

- 資訊推薦